現役時代には、電卓・時計用CMOS LSIをはじめS-RAMやROMチップ、オペアンプやD-A変換回路など全てCMOSチップのレイアウト設計(パターン設計)に関わってきました。

当時(1970年代後半から1980年代)はすべて手書きで、設計もチェックも大変でしたが、とてもいい勉強にはなりました。顕微鏡でチップの表面写真を見ればだいたいどんな回路なのか想像できます。それらの経験(少々古い話ですが今でも基本は変わってないと思う)を掲載していこうと思います。

思いつくままに掲載内容の項目を挙げてみました。

・ CMOSインバータの各種レイアウト設計法

・ 入力回路、出力回路のレイアウト設計法

・ 太い配線パターン(クラック対策)のレイアウト設計

・ パッケージストレス(MOS・gm のバラツキ)対策

・ 入力保護回路(静電破壊対策)のレイアウト設計

・ 出力保護回路(静電破壊対策)のレイアウト設計

・ オペアンプ設計(gmのバラツキ対策など)

・ 配線素子の使い方(PolySi配線、Al配線、拡散層配線)

・ コンデンサ、抵抗のパターン設計

・ 電源配線(電流分配)の配置法

・ クリティカルパス(配線の引回しと駆動回路の関係)

・ ガードバンド配置(ラッチアップ対策)

・ アナログ・デジタル混載チップのノイズ対策

・ 高速化・低消費電力化のためのレイアウト設計

・ .

・ .

上記の内容は変更することがあったり、掲載しない場合もあります。当然他に思い浮かべば追加もあります。1項目づつ掲載しますので完了するまでに数年かかるかも知れません。

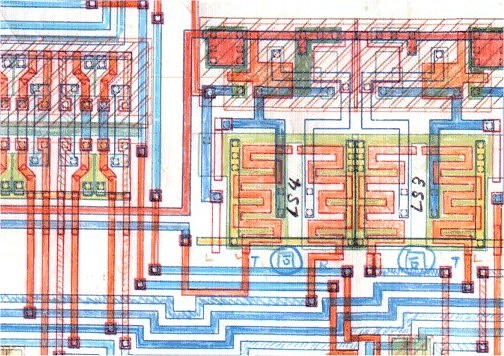

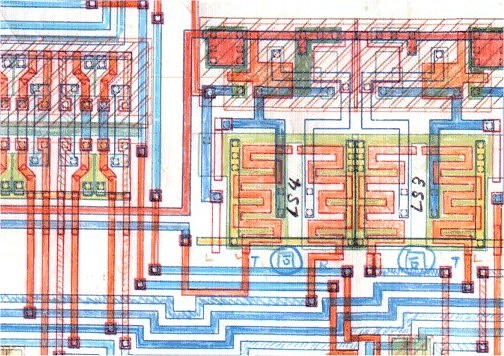

下図はCMOS LSI のレイアウトパターンです。

赤がポリシリコン、青がアルミ配線そして緑が拡散層です。

このパターン図では左部分が通常のインバータ回路、右側部分にレベルシフト回路(電圧変換)が配置されています。これらの回路構成が読める程度の知識があるとワンポイント講座も理解しやすいでしょう。

第1回 --> CMOSインバータの各種レイアウト設計法

第2回 --> CMOSレイアウト設計法(2)

第3回 --> CMOSレイアウト設計法(3)

第4回 --> CMOSレイアウト設計法(4)

第5回 --> CMOSレイアウト設計法(5)

|