静電破壊というのは文字通り静電気によってICやLSIのゲート酸化膜破壊や拡散層のジャンクション破壊、アルミ配線の溶断などの破壊現象をいいます。この静電気は、電圧にすると数100Vから数1000Vに達することが多く、このような高電圧がICなどの入出力端子に印加されると、IC内の回路や配線が破壊されることがある。 ICの静電破壊耐圧を評価する場合、主に2種類の方法がある。1つはHBM(Human Body Model)方式と呼ばれるもので、昔から使われている評価法である。これは人間自身にたまった静電気(数10PFから200PF程度)が、ICに触わることによりICに電荷が放出されICが破壊されるわけだが、その破壊耐圧で静電破壊強度を評価しようというものである。 2つめはCDM(Charged Device Model)方式と呼ばれるものである。最近は、ICのパッケージとしてプラスチックパッケージが増えてきましたが人間がICに触らなくても製造段階や搬送中に摩擦でICパッケージが帯電してチャージし、基板にセットする時や何かの導体にICのピンが接触した時に、チャージした電荷が放電されIC自身が破壊される現象が問題になっている。この耐圧を評価する方法がCDMである。評価するための電圧波形に関する暫定規格としてEIAJ,EOS/ESDがあります。

その他、静電破壊の原因として最近の製造プロセスに起因するものが上げられる。最近多く使われだした電子ビーム露光技術は、ウェーハ表面に帯電をもたらす。また、イオン注入等のイオンビーム加工による帯電、プラズマによるドライエッチング工程での帯電などは酸化膜に損傷を与え、歩留まり低下の要因として、重要課題になっている。

さて、CMOSデバイスの静電破壊対策ですが、基本的な話をまずしておきます。MOS構造のように非常に酸化膜が薄く、しかも入力インピーダンスが高いものは入力に過電圧が印加されるとゲート酸化膜が絶縁破壊するという危険性を常に持っている。絶縁膜(SiO2)の電界強度は約2X106(V/cm)と言われており酸化膜厚が0.05umの場合耐圧は約100(V)ということになる。(電界強度 E = V/d より)この耐圧は温度が上昇するとさらに低下する。

CMOSデバイスにおいては、主に入力端子と出力端子の静電破壊対策が重要である。入力端子に関しては、抵抗とクランプダイオードによる保護回路の構成がほとんどである。抵抗により印加ノイズをなまらせ、その間にクランプダイオードで電源端子などにリークさせる。従ってゲート酸化膜には直接高電圧は印加されないで保護される。ただ、ダイオードで流せる電流には限度があるので、印加ノイズの持つエネルギーが大きい場合は、ダイオードがジャンクション破壊をおこすことがある。このあたりは、ダイオードの大きさやレイアウトで対処できるので、各社それぞれノウハウを持っている。抵抗は1Kから10Kオーム程度が一般的であり、拡散層を使う場合と、ポリSiを使う場合がある。入力端子に関する静電破壊対策については、MOSの参考図書に多く掲載されているのでここでは、これ以上ふれない。

やっとここでの本題である出力端子の静電破壊について話をすすめます。出力端子の静電破壊に関しては、一般の参考書にはほとんど書かれていません。それは入力端子のような特別な保護回路というものがないからです。それではどうしているのかといいますと、出力端子はMOSのドレイン(拡散層)が接続されているので、クランプダイオードが自然に付く形になります。しかも出力回路は駆動能力を確保するために、比較的gmのおおきな設計になっていますので、出力端子の保護抵抗はほとんどありませんが、ドレイン容量(ダイオード面積)が大きいので、静電破壊に比較的強い。あとは各社のレイアウト設計法のノウハウで設計しているのが現状です。

そこでここでは私が20数年前(会社時代)に出願した出力端子の静電破壊対策の特許について紹介します。出願して20年過ぎたのでたぶん特許権は切れていると思います。 実際に試作し効果を確認した後、特許出願しました。当時これは有力特許になると社内で言われ外国出願までしましたが、その後有力特許として役に立っているのか(私は会社を辞めましたので)わかりません。

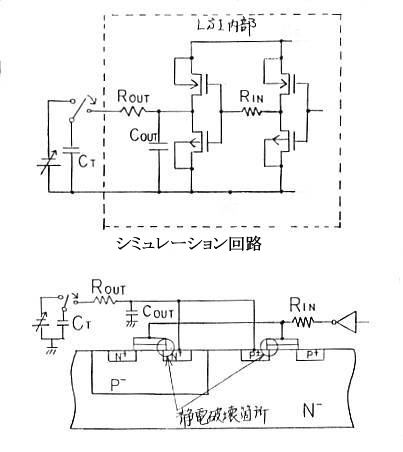

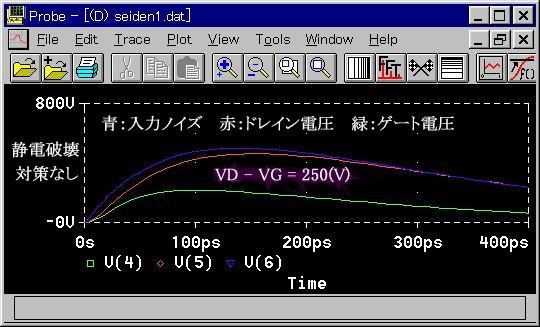

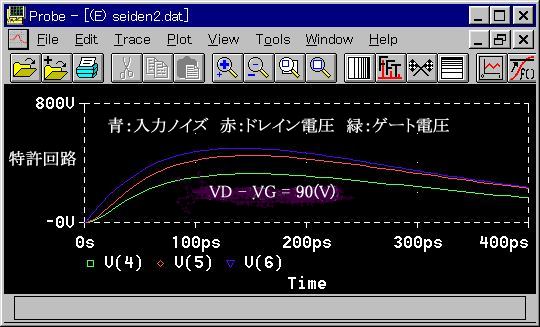

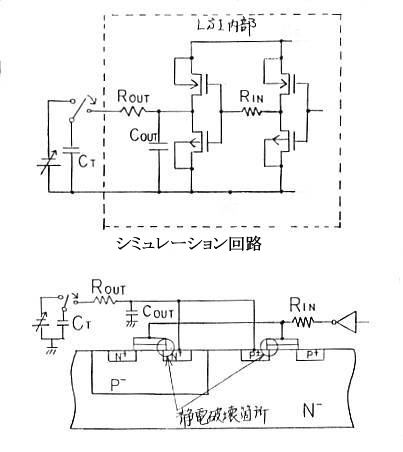

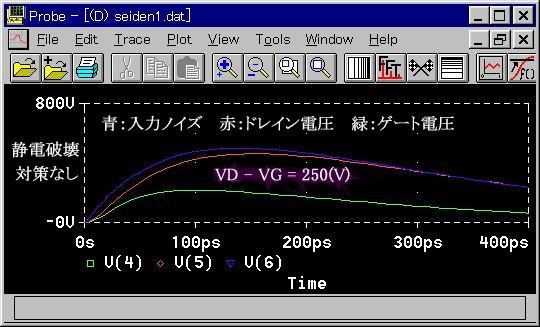

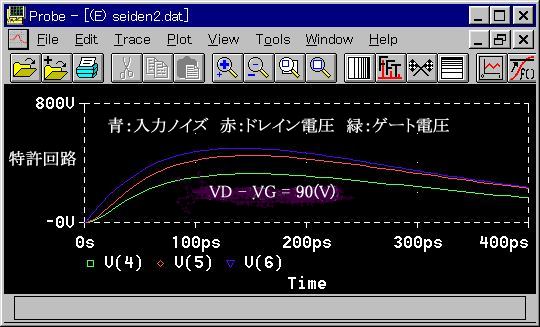

それではこのアイデアをシミュレーションで確認してみましょう。下図においてRinの抵抗値が50オームの場合と5KオームでMOSのゲートとドレインの電圧差が大きく違うことを下に示したシミュレーション結果で確認して下さい。

本ホームページで紹介しているSPICEなどのシミュレータを使って、静電破壊対策の新しい回路を考案すれば、企業が飛びつくでしょう。 |