|

丂恖娫偺擼偼栺侾侽倂偺僄僱儖僊傪徚旓偡傞偦偆偱偡丅堦曽俴俽俬偺悽奅偱偼丄儅僀僋儘僾儘僙僢僒偺徚旓揹椡偑恖娫偺俁攞埲忋偮傑傝俁侽倂傪墇偊傞帪戙偵側傝傑偟偨丅傑偨丄廃攇悢偱傒傞偲恖娫偺擼嵶朎偺僋儘僢僋廃攇悢乮恄宱僀儞僷儖僗乯偼丄 俇侽侽俫倸側偺偵懳偟偰嵟怴偺儅僀僋儘僾儘僙僢僒偼丄侾俧俫倸偵嬤偄摦嶌廃攇悢偵側偭偰偒傑偟偨丅

偙偺傑傑奺庬俴俽俬偺摦嶌廃攇悢偑崅偔側偭偰偄偗偽丄傑偡傑偡徚旓揹椡偑憹壛偟偰偄偔偙偲偼娫堘偄偁傝傑偣傫丅摿偵嵟嬤偺実懷婡婍偵偍偄偰偼丄僼儖壱摥俉帪娫乮夛幮偺嬑柋帪娫乯摦嶌偡傞偙偲偑丄彜昳偺廳梫側巇條偵側偭偰偄傑偡丅廬偭偰丄偙傟偐傜偺俴俽俬偺奐敪偺僉亅億僀儞僩偼丄掅徚旓揹椡壔媄弍偵偮偒傞偲巚偄傑偡丅崱屻奺庬掅徚旓揹椡壔媄弍偵偮偄偰傕僔儈儏儗亅僔儑儞偱斾妑偟側偑傜徯夘偟偰偄偔梊掕偱偡丅

崱夞偼丄堦晽曄傢偭偨掅徚旓揹椡壔媄弍傪徯夘偟傑偡丅娙扨偵尵偊偽丄晧壸梕検偺廩揹傪揹椡徚旓側偟偱峴偆偲偄偆傕偺偱偡丅棟榑揑偵偼揹椡僛儘偵偱偒傑偡丅偨偩摦嶌廃攇悢偑抶偄偲偐丄揹尮偼儔儞僾攇傪巊偆昁梫偑偁傞偲偐丄偄傠偄傠栤戣偑偁傝丄傑偩幚梡壔偝傟偰偄傑偣傫丅夞楬偺傾僀僨傾偵傛偭偰偼丄悽偺拞傪曄偊傞夋婜揑側掅徚旓揹椡壔媄弍偵惉傝摼偊傑偡丅傒側偝傫傕峫偊偰傒偰偔偩偝偄丅偦偺帪栶偵棫偮偺偑杮儂亅儉儁亅僕偱徯夘偟偰偄傞傛偆側僔儈儏儗亅僔儑儞僜僼僩偱偡丅

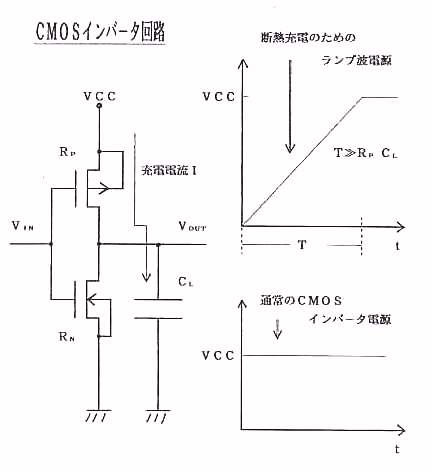

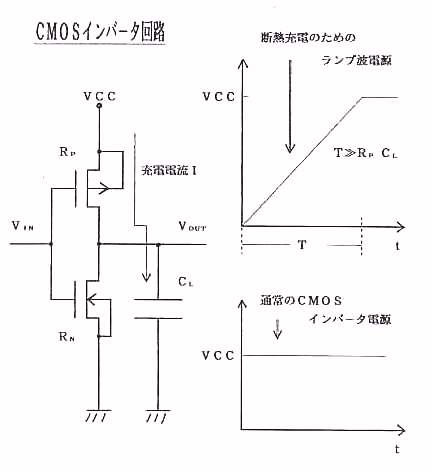

丂俠俵俷俽僀儞僶亅僞傪峫偊偨応崌乮壓恾嶲徠乯丄俹俵俷俽偵俴倧倵怣崋乮俧俶俢儗儀儖乯偑偔傞偲丄俹俵俷俽偑俷俶偟弌椡梕検俠L傪俫倝倗倛乮VCC揹尮儗儀儖乯偵廩揹偟傑偡丅偦偺帪俹俵俷俽偺掞峈惉暘偱壓婰幃偺僄僱儖僊亅傪徚旓偟傑偡丅

師偵丄弌椡梕検傪曻揹偡傞帪偼俶俵俷俽偱僄僱儖僊亅傪徚旓偟傑偡丅傑偨丄擖椡攇宍偺側傑傝偱丄娧捠揹棳偵傛傞徚旓揹椡傕柍帇偱偒傑偣傫丅偮傑傝尰嵼偺俠俵俷俽夞楬偺掅徚旓揹椡壔媄弍偼丄摦嶌廃攇悢傪壓偘傞丆揹尮揹埑傪壓偘傞丆弌椡梕検傪壓偘傞乮傑偨婑惗梕検傪尭傜偡乯丆娧捠揹棳傪尭傜偡丆夞楬揑偵岺晇傪嬅傜偡摍偺曽朄偟偐偁傝傑偣傫丅 偦偙偱丄弌椡梕検傪壓偘傞戙傢傝偵梕検傪廩揹偡傞帪偺丄僗僀僢僠偺掞峈惉暘偵傛傞揹椡懝幐傪柍偔偟偰傗傠偆偲偄偆偺偑丄偙偙偱徯夘偡傞抐擬廩揹偺尨棟偱偡丅捠忢偺俠俵俷俽夞楬偼丄夁搉揑偵掞峈惉暘乮俹俵俷俽乯偺椉抂偵崅偄揹埑偑偐偐偭偰揹椡傪徚旓偡傞偺偱偁傞偐傜丄掞峈惉暘偺揹埵嵎傪嬌椡彫偝偔偡傟偽丄揹椡懝幐偼彫偝偔弌棃傞偼偢偱偁傞丅棟榑揑偵偼僛儘偵弌棃傞丅 偙傟傪幚尰偡傞偵偼丄俠俵俷俽僀儞僶乕僞偵偍偄偰丄俹俵俷俽偺俷俶掞峈俼倫偲弌椡梕検俠L偺愊丄偮傑傝帪掕悢倲偵斾妑偟偰偐側傝挿偄帪娫俿偱棫偪忋偑傞揹尮乮儔儞僾攇揹尮乯偑昁梫偵側傝傑偡丅

偙偺儔儞僾攇揹尮傪巊偆偙偲偵傛傝丄俹俵俷俽偱徚旓偡傞僄僱儖僊乕偼丄壓婰幃偺傛偆偵尭彮偟傑偡丅

儔儞僾攇揹尮傪挿偔偡傟偽丄棟榑揑偵偼徚旓僄僱儖僊乕偼僛儘偵側傝傑偡丅偨偩丄抐擬廩揹偺曽朄偼丄備偭偔傝摦嶌偝偣偰廩揹帪偺懝幐僄僱儖僊乕傪尭傜偡曽朄偱偁傞偨傔丄嵟嬤偺崅懍壔偵偼岦偐側偄柺偑偁傞丅摦嶌廃攇悢偑掅偔丄戝暆側掅揹椡壔偑昁梫側暘栰偱棙梡壙抣偑弌偰偔傞壜擻惈偑偁傞丅 丂幚偼崱夞偼怗傟側偄偑丄偙偺抐擬廩揹傪巊偭偨夞楬偵揹椡嵞棙梡宆偺揹尮傪慻傒崌傢偣傞偲丄偐側傝幚梡揑側掅徚旓揹椡夞楬偑幚尰弌棃傞丅懡偔偺俠俵俷俽夞楬偑採埬偝傟偰偄傞丅揹椡嵞棙梡宆揹尮偺栚揑偼丄曻揹僄僱儖僊乕傪嵞傃揹尮偵夞廂偟偰巊偍偆偲偄偆偙偲偱偁傞丅堦斣娙扨側夞楬偑丄僐僀儖傪巊偭偨夞楬偱偁傞丅弌椡梕検偵拁偊傜傟偰偄傞惷揹僄僱儖僊乕傪慡偰丄僐僀儖偺帴婥僄僱儖僊乕偵戙偊偰傗傞丄偮傑傝曻揹偱幪偰傜傟傞僄僱儖僊乕傪揹尮偵夞廂偡傞夞楬偱偡丅偄偢傟偵偟偰傕丄偙傟偐傜偺揹巕婡婍偺掅徚旓揹椡壔偵峷專偱偒傞夋婜揑夞楬傪丄夞楬偺傾僀僨傾偟偩偄偱採埬偱偒傞壜擻惈偑偁傞丅

丂壓偵帵偟偨僔儈儏儗乕僔儑儞寢壥偼丄抐擬廩揹傪巊偭偨応崌偲丄偦偆偱側偄晛捠偺俠俵俷俽僀儞僶乕僞偺弌椡梕検廩揹帪偺俹俵俷俽偵棳傟傞幚岠揹棳傪斾妑偟偨傕偺偱偁傞丅揹尮埲奜偼慡偰摨堦忦審偱僔儈儏儗乕僔儑儞偟偰偄傑偡丅 |