A , B 間に時刻 t = 0 で大きさ $V_{IN}$ のステップ入力を加えた時の電圧Vの時間的変化は

$$V = V IN (1 - e^{t/RC})$$

VがVュ∾の90%に達する時間Tは

T = 2.3RC(s)

つまり配線パタ・ンの抵抗と容量の総量を計算して、それらの積を2.3 倍すれば遅延時間が概算できます。

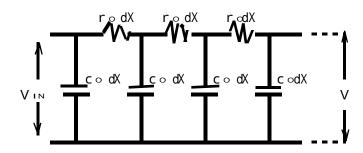

しかし実際には抵抗と容量は分布定数回路になっており、 図20のような回路で遅延時間を計算する必要がある。 配線の長さをd×の微少領域に分割し、微分方程式を立てて 解いてみる。

A , B 間に時刻 t = 0 で大きさ  $V_{1N}$ のステップ入力を加えた時の電圧 V の時間的変化は

$$V = V + \{1 - 4/e^{-(/4)(t/RC)}\}$$

VがV ™の9 0%に達する時間 Tは

T = 1.0R C (s)

配線自体の遅延としては集中定数回路で得られた2.3 RCではなく、1.0RCを使えばより正確であることがわかる。ICのパタ・ン設計者は、RC積の値で遅延時間を概算しながら設計を進めます。

r o , c o は単位長さ当たりの抵抗 , 静電容量 を表す。

## 図20 配線の分布定数回路

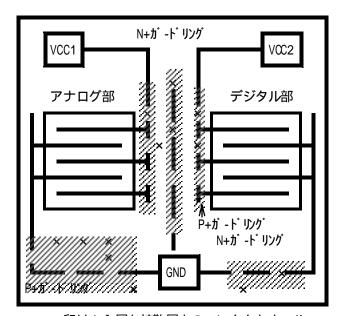

## (2)アナログ回路との混載

「CMOS回路では微細加工技術の進歩によりデジタル回路とアナログ回路の両方を混載して、1チップ化したLSIが増えてきた。

しかし混載した場合、デジタル回路のノイズがアナログ回路へ混入し、SN比が悪くなり誤動作を起こすことが考えられる。デジタル回路はパルスの変化点ごとに発生する雑音源であるので、充分な対策が必要である。

ノイズの原因は、貫通電流や消費電流による電源線の電位変動 (抵抗性によるものとインダクタンスによるものがある。), 寄生コンデンサによる信号のカップリングノイズ等があり、各々の原因に対してそれぞれ対策が必要である。

デジタル回路からアナログ回路へのノイズの混入経路 としては

電源線からのノイズ(A1電源配線やウェルなどを通して混入)

IC内のデジタル信号配線とアナログ信号配線間のカップリングノイズ

ICの入出力端子(パッド)やボンディングワイヤ並びにリ-ドフレ-ムのピン間のカップリングノイズ

### の対策としては、

電源配線を太くして配線抵抗を下げる。

デジタル用とアナログ用の電源配線をはっきり分けて 配置する。できれば電源端子も別々にする。

デジタル回路とアナログ回路のウェルを共通にしない。 (図21のP+ガ-ドリング)

基板に対しては電源に電位を固定するためのコンタクトを数多くとる。(図21のN<sup>+</sup>ガ・ドリング)

デジタル回路とアナログ回路の配置はなるべく離し、そ の間にはガ・ドリングを配して容量結合を妨げる。

# の対策としては、

デジタル配線とアナログ配線を並列に配置したり、交差させたりしない。どうしても並列配置する場合は、間に電位の固定した配線(例えば電源線)を配置したり、配線の距離を離す。

### の対策としては

デジタル端子とアナログ端子を隣接配置しない。また端子間に電位の安定したダミ - 端子(電源線と結線する)を配置する。

ボンディングワイヤ間やリ・ドフレ・ムのピン間の距離を離す。 **パッケ・ジ設計**

# ェヒチップ

×印はA 1 層と拡散層とのコンタクトホ - ル 上図はN基板, Pウェル構造の場合

## 図2 1 デジタル - アナログ混載ICのノイズ対策

## 6 . 参考文献

(1)WMペニ - 他; MO S集積回路, 近代科学社, 1977

(2) 香山 晋編; 超高速 MOSデバイス, 培風館, 1992